マイコンの構造と処理2

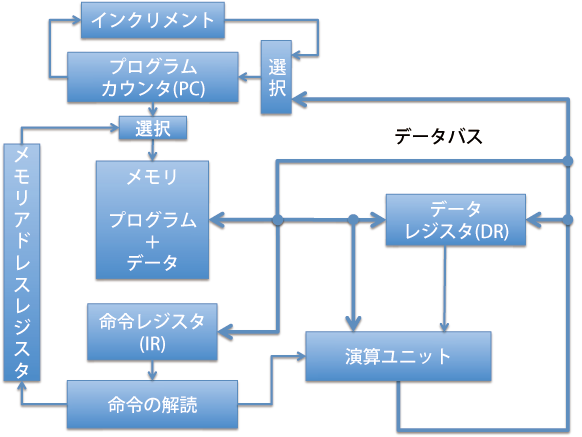

マイコンの内部構造をなるべく簡単に表現ものが図1である.マイコンを構成する3要素としては,CPU,メモリ,入出力装置である.図1のマイコンのモデルには,入出力装置は省略されている.また,メモリ以外の各部は,CPU内部に実装されているものである.図1のモデルは,大幅に簡略化されており,実際には,複雑な論理回路で構成されている.

まず,図中の各要素についてその役割を列挙しておく.

- プログラムカウンタ(PC)・・・カウンタ値が格納されており,その値は,プログラムが格納されたメモリのアドレスを意味している.通常,プログラムはカウンタ値の小さい方から順に実行されるため,プログラムカウンタの値をインクリメントすることで次の命令のアドレスを指し示すこととなる.電源投入直後は,プログラムカウンタは 0 である.

- 命令レジスタ(IR)・・・メモリから取り出された命令を格納するレジスタである.

- 命令の解読・・・メモリから取り出された命令がどのような命令であるかを判別して,演算に必要な制御信号を操作する役割をもつ.また,命令を解読することで,必要なデータのメモリアドレスが判るので,メモリアドレスレジスタへその値を格納する.

- 演算ユニット・・・解読された命令を元に制御信号により制御され必要な演算を実行する部分である.演算ユニットの出力はデータバスを介して各部へ伝達される.

- データレジスタ(DR)・・・メモリから取り出されたデータや演算ユニットからの出力結果を一時的に記憶するためのレジスタである.

- メモリアドレスレジスタ・・・命令を解読した際に,ジャンプ命令などの分岐命令の場合,次に実行する命令は,インクリメントされたプログラムカウンタの値とは異なる.メモリアドレスレジスタは,その値を格納しておき,プログラムカウンタの代わりにメモリアドレスを指し示すことになる.

- 選択・・・全体の制御において入力された値のどちらかを選択し出力する部分である.

- データバス・・・メモリとCPUを接続するバスである.プリンストンアーキテクチャの場合,プログラム(命令)とデータがこのバスを使ってやり取りされる.ハーバードアーキテクチャの場合は,データバスはデータのみを伝達させる.プログラム(命令)は別にバスが用意されている.

図1:マイコンの簡単なモデル

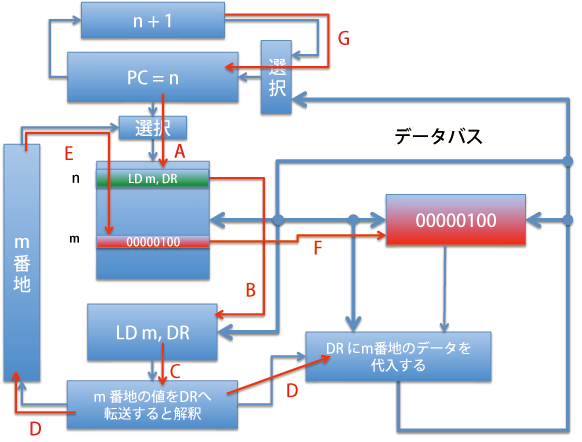

図1のモデルを使って,メモリからデータを読み出す手順を図2に示す.ここでは,具体的な例を示しながら説明する.メモリからデータを読み出すオペコードを LD として,それに続くオペランドを m, DR とする.m はデータが格納されているアドレス(ソースアドレス)を示す.DR は転送先のレジスタの名称である.

図2:メモリからのデータの読み出し

A:PCの値(n 番地)をメモリに渡し,PCの値をアドレスと見立てて当該アドレスの命令を特定する.この場合,「LD m, DR」である.

B:命令が特定できるので,その命令をデータバスを介して,IRに格納する.

C:IRに格納された命令を解読ユニットに送り,命令の解読を行う.解読により,演算に必要な信号線を変化させて回路を制御する.この場合,オペコードが LD なので,転送命令であると解釈し,それに続くオペランドが m, DR なので,m 番地のデータをDR へ転送すると解釈できる.

D:命令の解読結果で,データアドレスが判別できるので,そのアドレス値(m)をメモリアドレスレジスタへ格納すると共に,演算ユニットの制御も行う.

E:メモリアドレスレジスタの値(m)をメモリのアドレスとして,データ領域のデータを特定する.この場合,2進数で,00000100 である.

F:制御信号により,メモリのデータ領域からデータを取り出し,データバスを介してデータレジスタへ格納する.

G:命令はデータをロードする命令なので,PCの値はインクリメントされた値を次の命令のアドレスとして,次の命令を実行することになる.

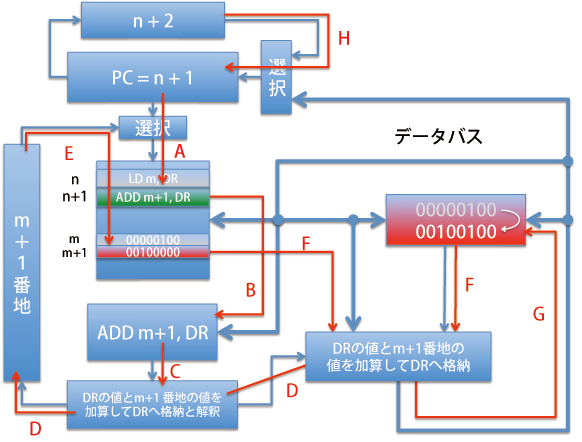

次に,ロードしたデータを使って演算させる手順を図3を使って説明する.ここでは,演算として加算を例にあげる.オペランドを ADD として,オペコードを m+1, DR とする.つまり,DR に格納されている値(00000100)とm+1 番地の値を加算して,DR に格納するという動作になる.

図3:データを使った演算

A:PCの値(n+1)をメモリに渡し,カウンタ値をアドレスと見立てて当該アドレスの命令を特定する.ここでは,「ADD m+1, DR 」である.

B:命令が特定できるので,その命令をデータバスを介して,IRに格納する.

C:IRに格納された命令を解読ユニットに送り,命令の解読を行う.解読により,必要な信号を変化させて回路を制御する.ADD は加算命令なので,演算ユニットに対して加算するように制御を行う.

D:命令の解読結果で,データアドレスが判別できるので,そのアドレス値(m+1)をメモリアドレスレジスタへ格納すると共に,演算ユニットの制御も行う.

E:メモリアドレスレジスタの値(m+1)をメモリのアドレスとして,データ領域のデータを特定する.この場合,2進数で,00100000 である.

F:制御信号により,メモリのデータ領域からデータを取り出し,データバスを介して演算ユニットへ転送するとともに,データレジスタのデータも演算ユニットへ転送する.

G:制御信号により解読された命令を演算ユニットで演算し,その結果をデータバスを介して再び,データレジスタへ格納する.本例では,00100100 がDR に格納される.

H:命令は演算命令なので,PCの値はインクリメントされた値を次の命令のアドレスとして,次の命令を実行することになる.

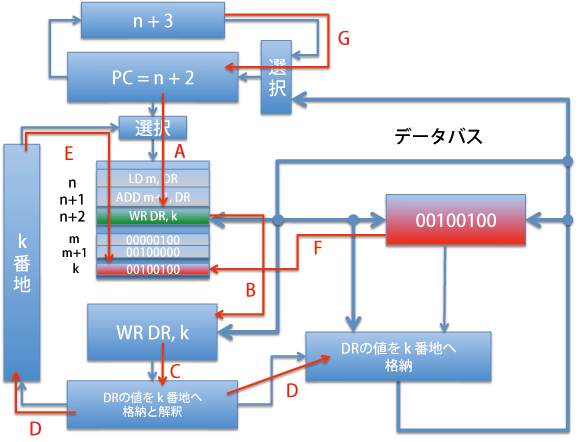

上記の手順で,演算結果は,データレジスタに格納されていることになる.次は,このデータレジスタの値をメモリへ格納する手順を示す.図4がその手順となる.ここでは,オペコードを WR とする.オペランドは,DR, k として,DR のデータをkで指定したアドレスの場所に格納する動作を行う.

図4:データのメモリへの書き込み

A:PCの値(n+2)をメモリに渡し,カウンタ値をアドレスと見立てて当該アドレスの命令を特定する.ここでは,「ADD m+1, DR 」である.

B:命令が特定できるので,その命令をデータバスを介して,IRに格納する.

C:IRに格納された命令を解読ユニットに送り,命令の解読を行う.解読により,必要な信号を変化させて回路を制御する.

D:命令の解読結果で,データアドレスが判別できるので,そのアドレス値をメモリアドレスレジスタへ格納する(ここでは k である)と共に,演算ユニットの制御も行う.

E:メモリアドレスレジスタの値をメモリのアドレスとして,データを格納するアドレスを特定できる.

F:命令の解読からの制御信号により,データレジスタに格納されているデータをメモリ内の上記Eで確定したアドレスの領域に格納する.

G:命令はデータの転送命令なので,PCの値はインクリメントされた値を次の命令のアドレスとして,次の命令を実行することになる.

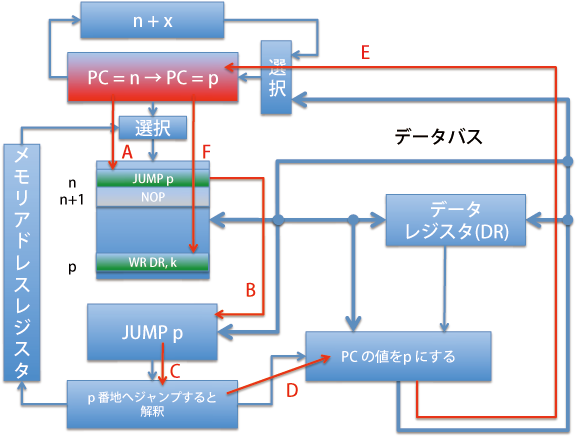

次は,これまでとは異なり,PCがインクリメントされない例を示す.この例は,ジャンプ命令の例である.オペランドを JUMP ,オペランドを p とする.動作としては,この命令が実行されると,次に実行される命令が p 番地の命令となる.

図5:ジャンプ命令を実行したとき

A:PCの値(n)を元に,メモリから命令アドレスを決定する.

B:特定された命令をIRに転送する.

C:IRの命令を命令の解読へ転送する.解読結果として,p 番地へジャンプする命令であることがわかる.

D:命令を解読して制御信号を生成し,回路を制御する.今回は,ジャンプ命令であるので,メモリアドレスレジスタへは何も格納されない.

E:メモリからのデータの転送もメモリへのデータの転送も行われない.演算ユニットでも何も行われないが,制御信号により,ジャンプ先のアドレスがPCにセットされる.つまり,インクリメントされていたPCの値(n + x) は不要で,ジャンプ先のアドレス値(p)がセットされることになる.

ここでは,マイコンの簡略化モデルを使って,命令の実行手順について説明した.マイコンは,プログラムカウンタ(PC)を使って,メモリに格納された命令のアドレスを指定しており,その命令を取り出して命令レジスタ(IR)に格納している.その後,命令を解読して,命令に応じた制御を行っている.

命令によっては,データをメモリに書き込んだり,データをメモリから読み出しするため,メモリアドレスレジスタを使用することもある.さらに,演算結果をデータレジスタ(DR)に書き戻す動作も行う.また,ジャンプ命令の場合は,インクリメントされたPCの値ではなく,ジャンプ先のアドレスがPCに格納されてメモリの命令アドレスを指し示す場合もある.

つまり,命令の実行では,次の動作を必ず行うことになる.

- メモリから命令を取り出しIRに格納

- IRに格納された命令を解読し回路を制御

- 命令に応じた演算を実行(ここでの演算とは,四則演算や論理演算のみだけでなく,データの読み出しやデータの格納も演算として扱われる)

これら3つの動作はどの命令であっても必ず行われる.そして,命令によっては,次の動作を行う場合もある.

- メモリに対するアクセス

- レジスタに対するアクセス

命令を実行するという行為は,マイコンの内部では上記のような動作を行っているということである.