マイコンの構造と処理3

「マイコンの構造と処理2」の最後で,マイコンにおける命令の処理手順を示した.どんな命令であっても下記の3つの工程は必ず行われる.

- メモリから命令を取り出しIRに格納(Instruction Fetch:IF)

- IRに格納された命令を解読(Instruction Decode:ID)

- 命令に応じた演算を実行(Execute:EX)

また,命令によっては,次の工程を伴う場合もある.

- メモリに対するアクセス(Memory Access:MA)

- レジスタに対するアクセス(Write Back:WB)

命令は,上記のIF, ID, EX, MA, WB の工程を経て実行される.

マイコンの内部は論理回路で構成されている.命令を実行する各工程の回路は独立しており,それぞれの工程をある程度並列に処理できる.ベルトコンベアのようにある命令が流れて行き,各工程で加工が施されていく.つまり,ID 工程の最中に IF の工程を実施することが可能なのである.これをパイプライン処理と呼び,マイコンで命令を実行するうえで大変重要な処理手順なのである.

本ページでは,主にこのパイプライン処理について説明する.

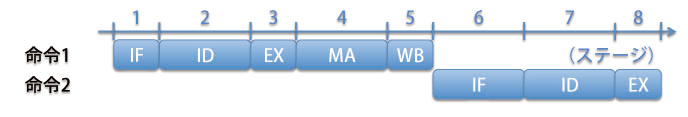

図1は,CISCの命令セットアーキテクチャの実行例である.CISCは命令長が可変長であるため,それぞれの工程でのステージの長さ(処理時間)は命令により異なることが多い.図1の例では,2つの命令を実行するのに,8ステージを費やしている.

各ステージの処理時間については,この後に説明する.

図1:CISC命令の実行

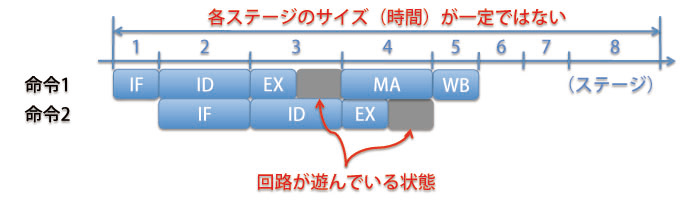

図1の2つの命令の実行にパイプライン処理を導入した例が図2である.それぞれの工程は独立しているため,図2のように各ステージで異なる工程を並列して実施できる.しかし,命令によってステージの長さが異なるため,工程終了後も次の工程に移ることができず,待ち時間が発生してしまう.

上述したように,ベルトコンベアのように命令が流れてきて,各工程の処理が施されて次の工程へ渡される.そのため,次の工程が終了していなければ命令を次の工程へ送ることはできない.そのため,工程ごとに処理の足並みを揃える必要があるのである.

CISCの命令セットアーキテクチャを採用しているマイコンにおいては,パイプライン処理を導入するメリットが少なく,導入されていないものもある.

図2:CISC命令のパイプライン処理

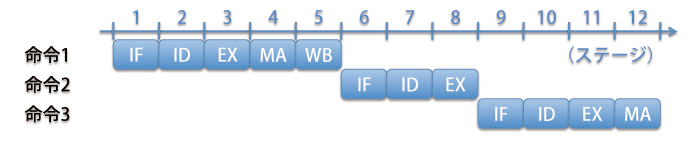

RISC命令セットアーキテクチャの場合,全ての命令は同じ長さであるため,命令を実行する際の各工程のステージの長さは全て同じになる.図3は,RISCにおける命令の実行を図示したものである.

命令によっては,MA や WB 工程もある.図3では,3つの命令を実行するために12ステージを費やしている.

図3:RISC命令の実行

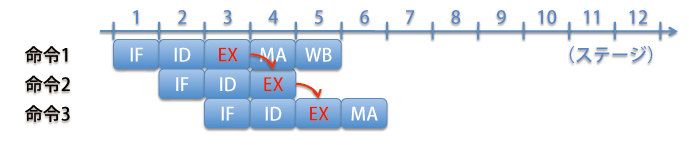

RISCは,全ての命令が同じ長さで,各ステージが全ての工程において同じ長さで実施できるため,図4のように,各工程の並列実施を考慮してパイプライン処理を導入することができる.図4は理想的なパイプライン処理である.図3で12ステージ費やしていた3つの命令が6ステージで全て完了していることがわかる.

図4:理想的なパイプライン処理

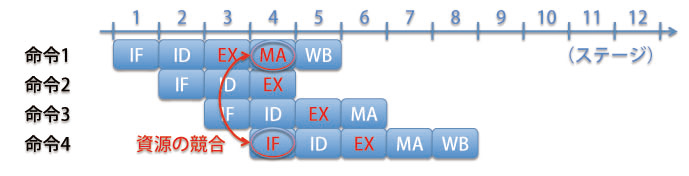

しかし,図4のような理想的なパイプライン処理が続くわけではない.「マイコンの構造と処理2」で説明したように,命令やデータは,データバスを介してやり取りされる.そのため,命令を取り出す IF と MA の工程を同時に行うことができない.つまり,データバスが1つであるため,並列に処理できないということである.このようなハードウェアの構造に起因するパイプラインの乱れを「構造的ハザード」と呼ぶ.

図5:パイプラインの構造的ハザード

構造的ハザードは,ハードウェアの問題なので,ハザードが発生しないようなハードウェアアーキテクチャであればこの問題は解消される.例えば,ハーバードアーキテクチャのような命令とデータが別々のメモリに格納され,それぞれ独立したバスを利用するとすれば,このような問題は発生しない.

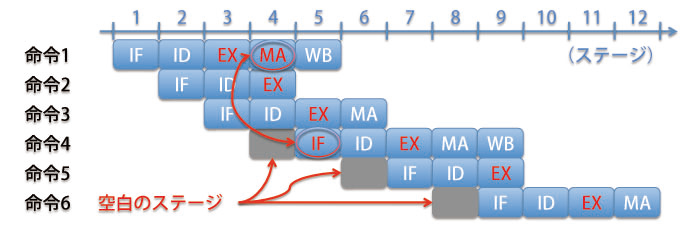

しかし,ハードウェアの改良は設計の複雑度を増し,ハードウェアの規模を拡大させる.これにより構造的ハザードが完璧に解消されるわけではないので,このハザードがあることを前提として,図6のような処理を施し,パイプライン処理を若干乱すことを行う.

図6:構造的ハザードによるパイプラインストール

図6は,構造的ハザードを回避するためにパイプライン処理を若干崩している例である.つまり,各工程で同一のハードウェア資源を利用するとき,パイプラインを1ステージずらして競合しないようにするのである.これをパイプラインストールと呼ぶ.

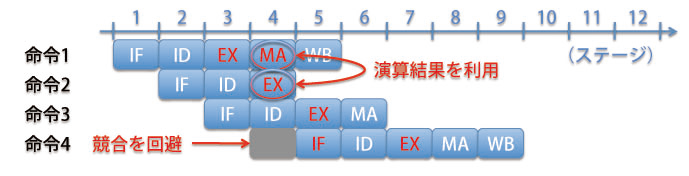

ハードウェアアーキテクチャが原因で発生するパイプラインストールの他に,データによるパイプラインストールのハザードがある.それは,図7にあるように,次の命令の実行に直前の命令のデータを使う場合である.

図7の場合,命令2を実行するとき,命令1の実行結果を使うことを考えている.つまり,命令2をこのタイミングで実行させることはできない.

図7:パイプラインのデータハザード

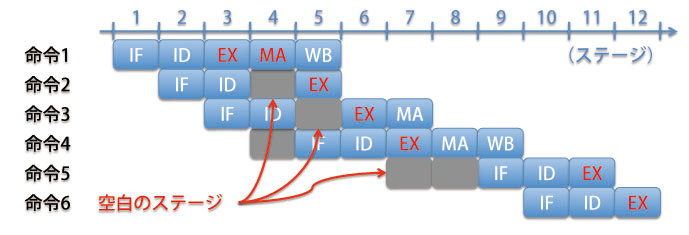

そこで,図8のように,パイプラインをストールさせて,タイミングをはかるのである.

図8:データハザードによるパイプラインストール

これもパイプラインストールであるが,原因が違う.一口にパイプラインストールと言っても,ハードウェアアーキテクチャが原因の構造的ハザードによるパイプラインストールとデータハザードによるパイプラインストールが存在するのである.

パイプラインストールは,パイプライン処理のステージ内に空白ステージを作ることになるので,別名,パイプラインバブルとも言われている.

このパイプライン処理は,CISCより,RISCアーキテクチャへの導入の方が効率化をはかるうえで大変有効である.また,ハードウェアアーキテクチャでは,プリンストンアーキテクチャよりデータバスと命令バスが独立しているハーバードアーキテクチャの方が効率化の点では大変有効な処理である.

このパイプライン処理を2つ用意し,2つの命令を同時にパイプライン処理する方法をスーパースカラと呼ぶ.これを実現するためには,IF, ID, EX などの各工程を実施する回路ユニットが2つずつ必要となり,回路規模としてはかなり大きくなるが,かなり高速に処理できるという利点がある.

以上がパイプライン処理についての説明である.なるべくパイプラインを乱さないように処理することが大切であり,構造的ハザード,データハザードの他にもさまざまな要因でパイプラインストールが起こるがここではこの程度に留めておく.

今回の説明では,5つの工程を5つのステージで実行する例を示した.これを5段パイプラインなどと呼ぶ.最も短いものは,PICなどで実装されている2段パイプラインである.多いものは数十段のパイプラインも存在する.

いずれも,パイプラインストールが発生する可能性があり,これをなるべく少なくする工夫が多くのマイコンで施されている.

マイコンの構造と処理の最後として,マイコンの処理時間について説明する.ここでは,パイプライン処理を行っているという前提で説明する.

命令の実行にはいくつかの工程があり,各工程ごとにステージが存在する.そもそも,マイコンは,入力されたクロックに同期して動作する同期型の論理回路であるため,このクロックを無視することはできない.

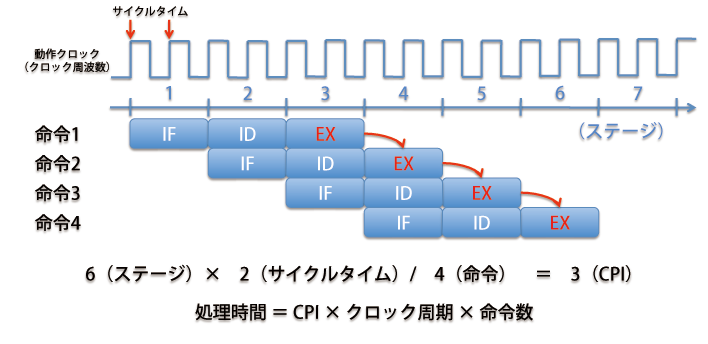

動作クロックの一周期をサイクルタイムと呼ぶ.工程を実行する各ステージの長さは,このサイクルタイムに支配されている.図9の場合,1ステージは,2サイクルタイムである.

理想的なパイプライン処理で命令が実行されているとすると,図9の場合,4つの命令で6ステージ費やされている.そして,1ステージは,2サイクルタイムなので,1命令の平均実行サイクルは,6 × 2 ÷ 4 = 3 となる.この値は,CPI(Cycles Per Instruction)と呼ばれ,1命令の平均的な実行時間を意味している.

図9を例にして,動作クロックが10MHzのときを考える.クロックの1周期は,0.1μsとなるので,処理時間は,3 × 0.1 × 4 = 1.2 [μs] と計算により求められるのである.

マイコンの処理速度を向上させるためには,CPI を小さくすること.動作クロックを速くすること.処理の命令数を減らすことが大切である.

マイコンの処理速度を表す単位として,MIPS(Million Instruction Per Second)がある.これは,文字通り,1秒間に実行できる命令の数であるが,ミリオンなので,百万単位であることに注意が必要である.1分間で6000万の命令を実行できるのであれば,それは,1秒間で100万命令をなので,1MIPSと呼ばれる.

近年では,FLOPS(Floating-point Operations Per Second)という浮動小数点を実行する命令回数を数える単位が使われる.浮動小数点演算はマイコンにとっては非常にサイクルを消費する演算なのである.このようなある種面倒な命令を1秒間に何回行うことができるかで,そのマイコンの性能を評価する方法もある.

マイコンにおけるプログラムの処理速度の向上は,開発者にとっては切実な問題である.上述してきたように,パイプライン処理におけるストールを軽減させるだけではなく,プログラムのアルゴリズムそのものの改善も処理速度の向上へつながる.

しかし,プログラムには,アルゴリズムとは無関係で必ず行わなければならない処理も含まれている.そのため,アルゴリズムが改善されて処理速度が10倍速くなったとしても,それ以外の処理の時間が含まれているため,一定時間以上の平均処理速度の改善は見られない.

例えば,あるプログラムで実行したときの処理時間が50秒であったとする.このうち80%は改善の余地があり,残りは改善の余地がないものとする.改善の余地があるプログラムを見直して,処理速度が2倍になったとすると,元々の処理時間は,50秒の80%なので,40秒が改善の余地がある部分である.処理時間が2倍になったので,改善後の処理時間は,20秒となる.もともと改善の余地のないプログラムが20%あったので,10秒は必ず費やすことになる.つまり,改善後の平均処理時間は,20 + 10 = 30 [秒] となり,元々の処理時間の60%程度の処理時間で実行できる計算となる.

プログラムそのものは,処理速度が2倍になったにも関わらず,全体としては,50%の改善にはつながらないのである.これを「アムダールの法則」と呼ぶ.

より詳しく勉強したい方は下記の文献を参照のこと.

- コンピュータアーキテクチャ (IT Text),内田 啓一郎 (著), 小柳 滋 (著)

- コンピュータ設計の基礎知識―ハードウェア・アーキテクチャ・コンパイラの設計と実装,清水 尚彦 (著)

- コンピュータの構成と設計 第3版「別冊」歴史展望,David A. Patterson/John L. Hennessy (著), 成田 光彰 (翻訳)

- コンピュータアーキテクチャのエッセンス (IT Architects Archiveシリーズ),ダグラス・E・カマー (著), Douglas E. Comer (著), 鈴木 貢 (翻訳), 中條 拓伯 (翻訳), 仲谷 栄伸 (翻訳), 並木 美太郎 (翻訳)

- 基礎から学ぶコンピュータアーキテクチャ,遠藤 敏夫 (著)

- コンピュータ設計の基礎 (マイコミジャーナルブックス),Hisa Ando (著)

演習問題

- ノイマン型コンピュータの説明として正しいものを1つ選べ.

- プログラムとデータが同一メモリに存在している

- プログラムを記憶できるプログラム内蔵型のコンピュータである

- プログラム用のメモリとデータ用のメモリが独立に存在している

- マイコンとアドレスバス24本,データバス16本で接続されているメモリのメモリサイズが何バイトであるかを求めよ.

- CISCとRISCの説明文として正しいものを1つ選べ.

- CISCは,命令を単純なものだけにして,複雑な命令を排除した命令セットアーキテクチャである

- RISCは,複雑な命令を持たせ,1つの命令でより複雑な処理を行わせるような命令セットアーキテクチャである.

- RISCは,歴史的にみればCISCに比べ新しく,RISCという呼び名に対してそれまでの命令セットアーキテクチャをCISCと呼ぶ.

- 4バイトデータの0x28943256をリトルエンディアンでメモリに格納するとき,正しく格納されているものを1つ選べ.ただし,左から右へメモリのアドレスは大きくなるものとする.

- 0x28, 0x94, 0x32, 0x56

- 0x65, 0x23, 0x49, 0x82

- 0x56, 0x32, 0x94, 0x28

- プログラムカウンタの役割や動作として誤っているものを1つ選べ.

- プログラムカウンタは,プログラムメモリのアドレスを示している

- プログラムカウンタは,電源の投入直後は,0 となっている

- プログラムカウンタは,命令によってはデクリメントされることもある

- パイプラインストールを引き起こす可能性のあるハザードとして誤っているものを1つ選べ

- 構造的ハザード

- モラルハザード

- データハザード

- 各ステージが1サイクルタイムで,12ステージで8命令が実行される理想的パイプライン処理があるとき,1命令が実行されるCPIを求めよ.

- 20MHzで動作するマイコンにおいて,CPI が 4.25 の命令が16個あるとき,このプログラムの処理時間を求めよ.

- あるプログラムの処理時間が48秒であったとき,改善の余地があるプログラムが52%であった.この部分を改善し,処理速度が4倍になった.改善後のこのプログラムの処理時間を求めよ.